Beyond the Silicon: How Talos Redefines AI Inference with FPGA Brutalism

A deep architectural analysis of the custom hardware accelerator that challenges the very foundations of flexible, software-driven deep learning.

Published: March 4, 2026 | Category: Technology | Analysis: Hardware & AI

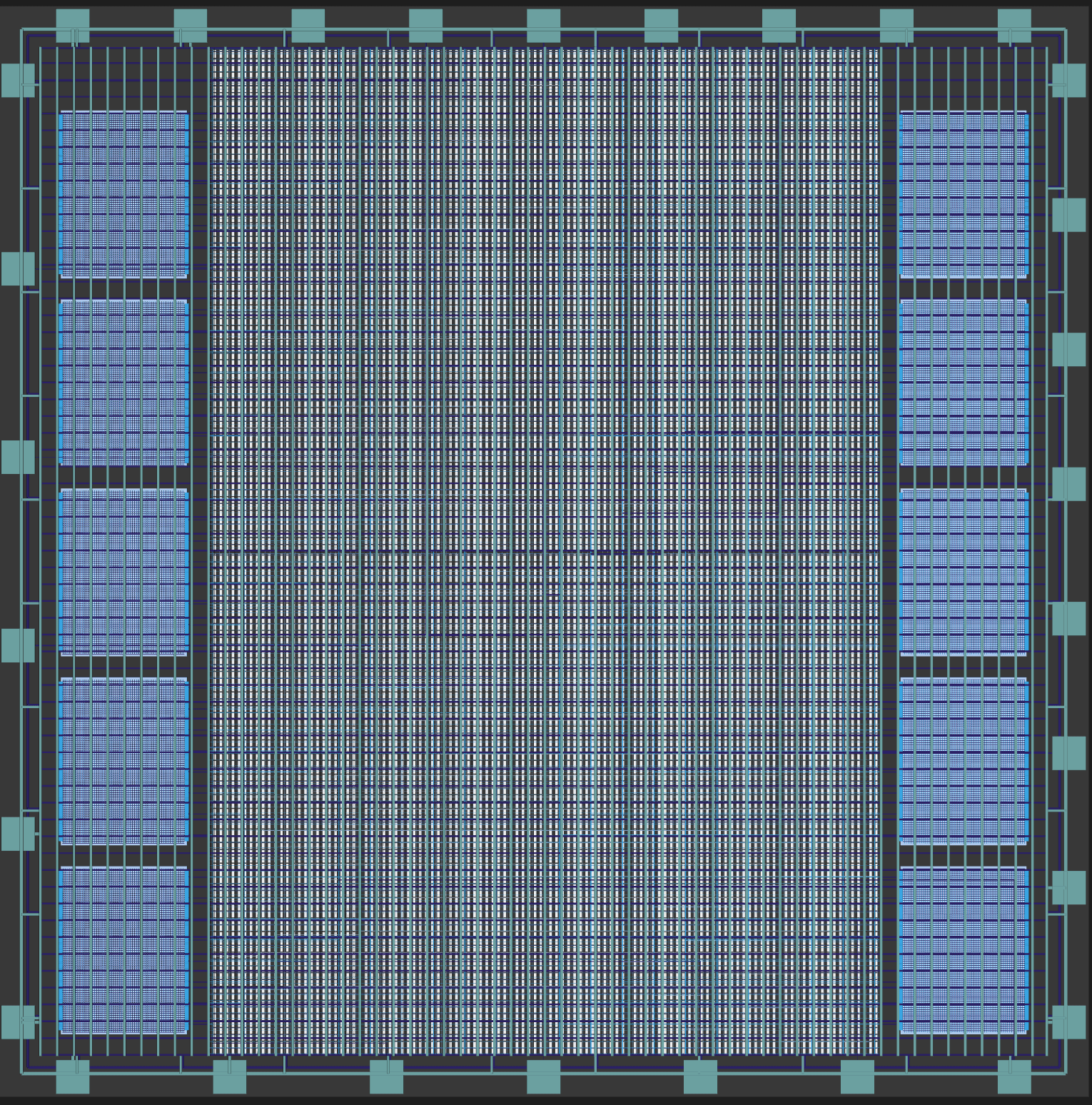

The unveiling of "Talos" by researchers Krish Chhajer and Luthira Abeykoon isn't merely another entry in the crowded field of AI accelerators. It represents a philosophical manifesto etched in SystemVerilog—a deliberate, almost brutalist rejection of the software-centric paradigms that have dominated deep learning for over a decade. This custom FPGA-based engine for Convolutional Neural Network (CNN) inference forces us to ask a fundamental question: In the relentless pursuit of flexibility, have we sacrificed the raw, deterministic power that only dedicated hardware can provide?

This analysis moves beyond the project's technical documentation to explore the broader implications of Talos's design philosophy, the grueling reality of hardware creation it exposes, and its potential ripple effects across edge computing, robotics, and high-frequency inference applications.

Key Takeaways

- Philosophy Over Performance: Talos is built on a "hardware-first" doctrine, stripping away runtime overhead, schedulers, and dynamic graphs to achieve cycle-accurate determinism—a stark contrast to frameworks like PyTorch.

- The Debugging Chasm: The project highlights the profound gulf between software and hardware development, where "debugging" involves negotiating with physics and chasing nanosecond timing violations in waveform viewers.

- Targeted Efficiency, Not Generalization: It sacrifices the broad flexibility required for training to achieve extreme efficiency for a specific task: fixed-architecture CNN inference. This makes it a potent solution for deployed, production-scale models.

- FPGA as a Strategic Middle Ground: Talos leverages FPGAs not as a stopgap before an ASIC, but as the ideal substrate for its philosophy—reconfigurable enough for design iteration but hardware-like enough to enforce physical constraints.

- A Bellwether for Specialization: The project signals a growing trend towards "disaggregated AI," where the one-size-fits-all GPU/software stack is fragmented into specialized, task-optimized hardware.